1、新建工程

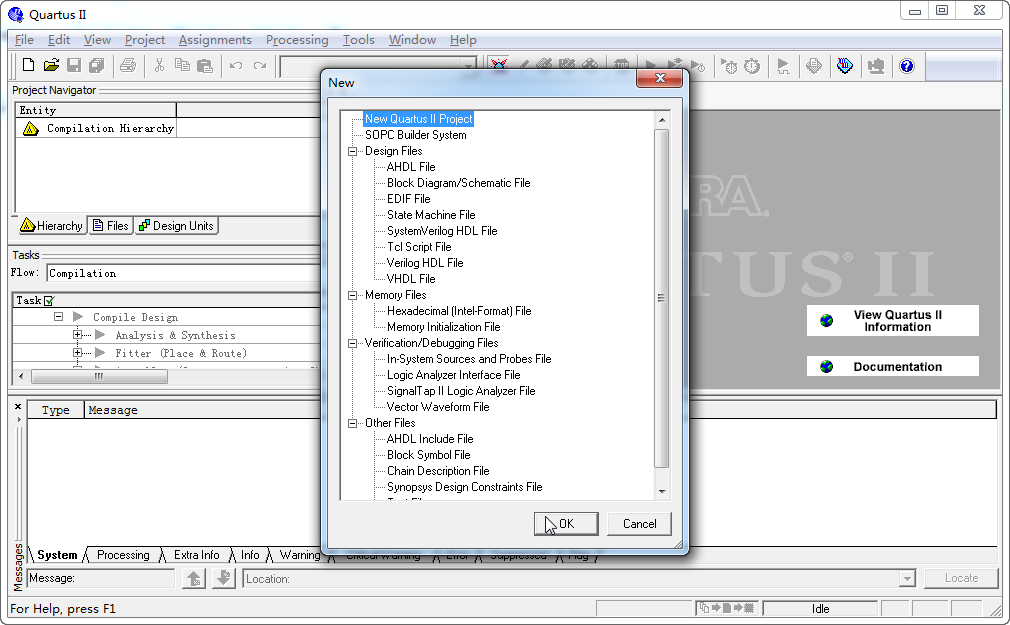

菜单File-New,新建工程。新建的工程最好放在一个独立的文件夹中。

添加已有文件至工程,可不选择

选择芯片型号

2、新建文件

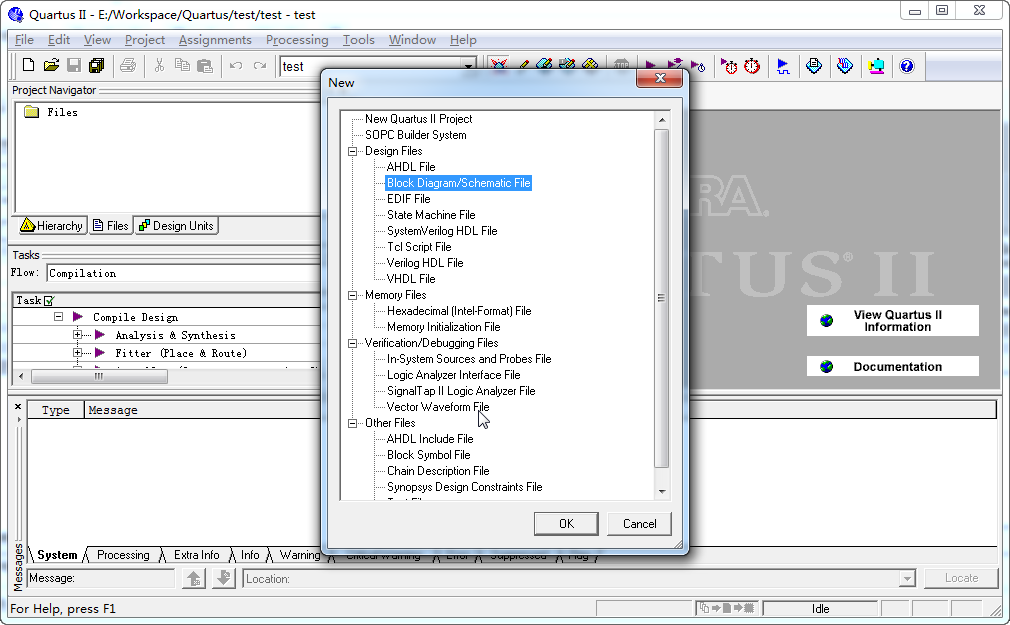

菜单File-New,可选择设计文件:Block Diagram/Schematic File(框图/电路图) / VHDL File / Verilog HDL File …,仿真文件:Vector Waveform File 等。

3、设计

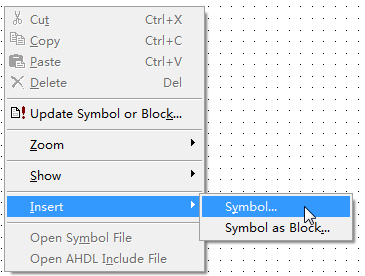

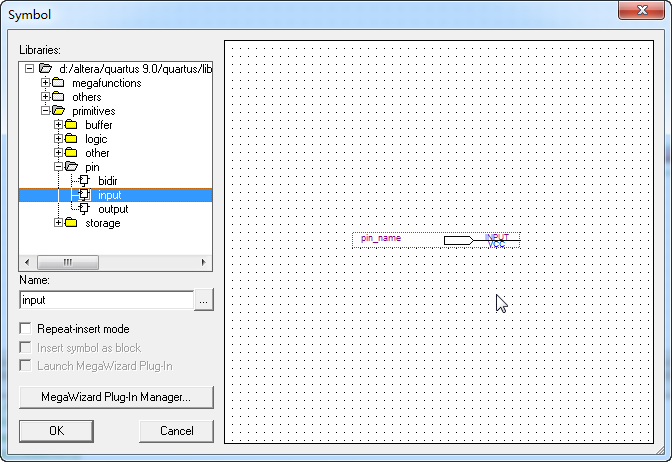

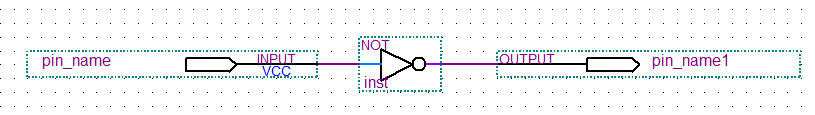

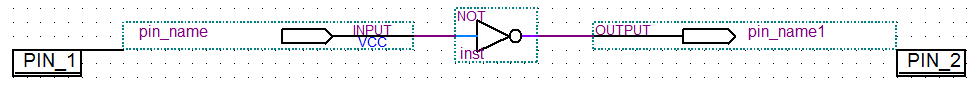

电路设计:插入器件,连接电路

电路设计,给每个管脚取名(非门,输入管脚,输出管脚)

紫色三角按钮用于综合(编译),蓝色三角按钮用于仿真

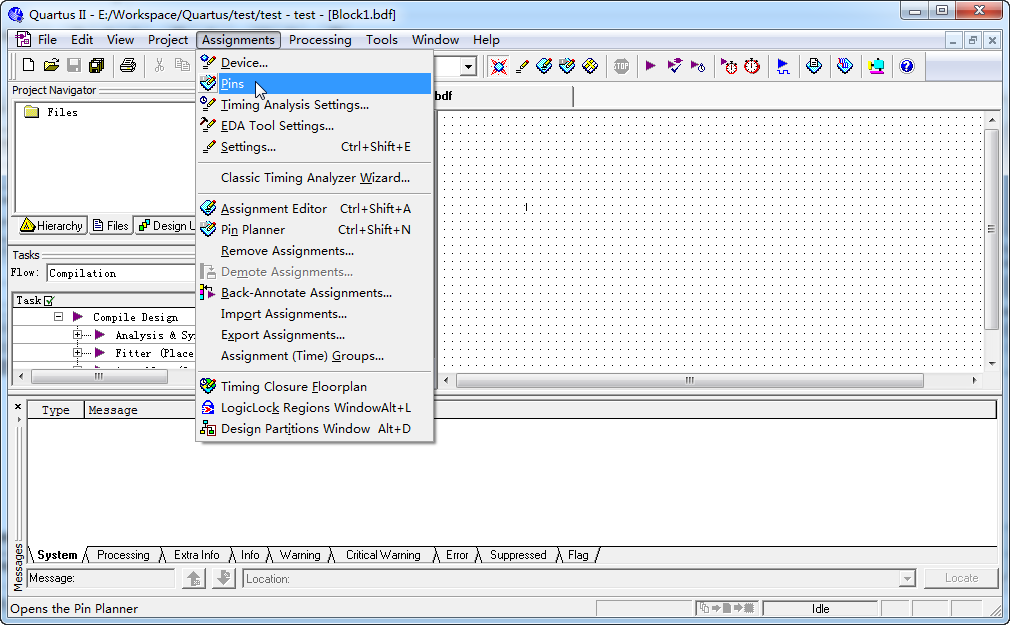

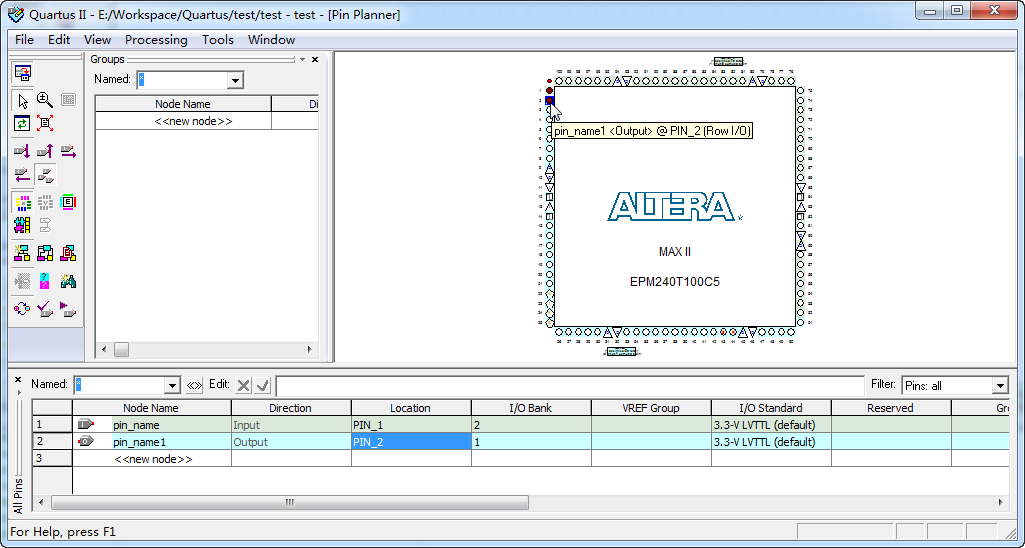

4、管脚分配

在Location中选择管脚即可,IOBank为管脚的分组编号

分配好管脚就会显示在电路图中(分配完管脚需要重新综合,才可以下载到板子中)

5、软件仿真

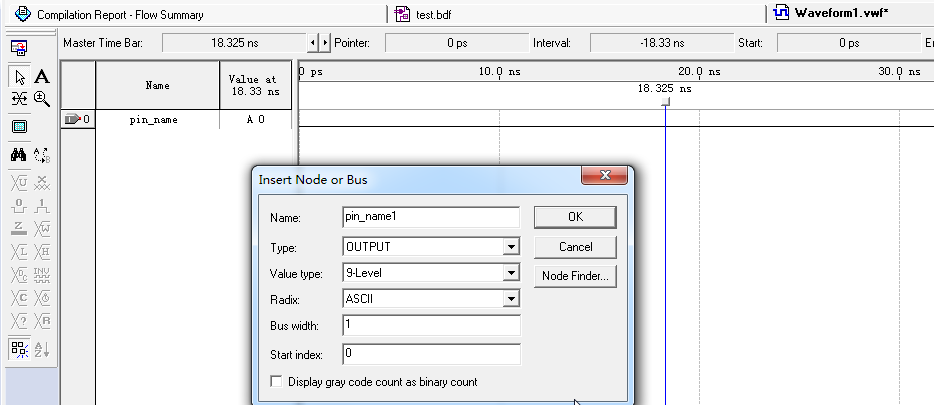

新建仿真文件:Vector Waveform File

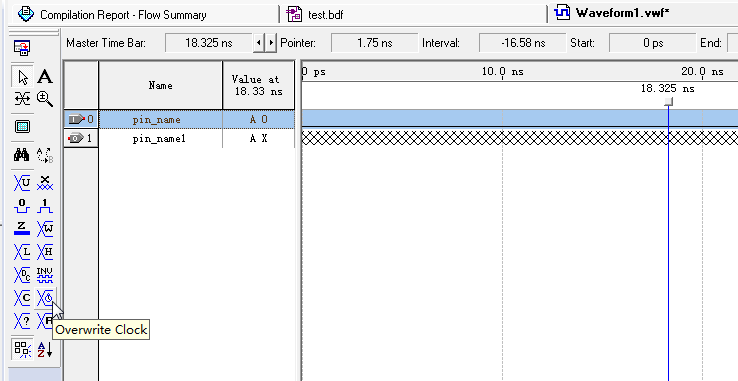

双击左侧空白处添加节点,输入节点名,会自动识别节点类型。点击OK添加。

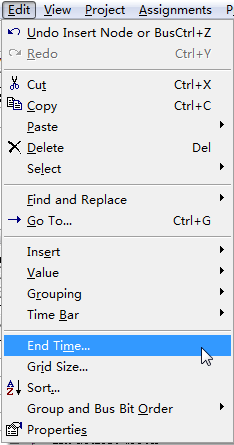

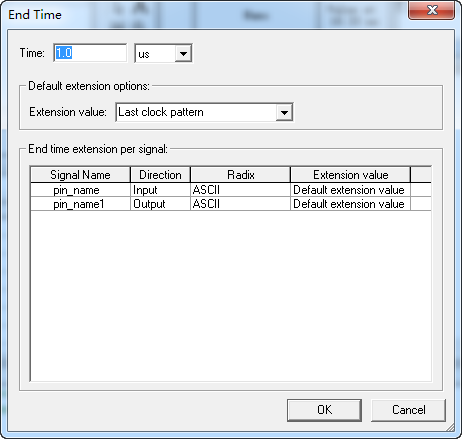

选择菜单Edit–End Time可以设置仿真时间长度

选中某个节点,或在右边的波形图上选中节点的某个时间段,点击左侧按钮可以设置输入的信号,例如时钟信号、高低电平等。

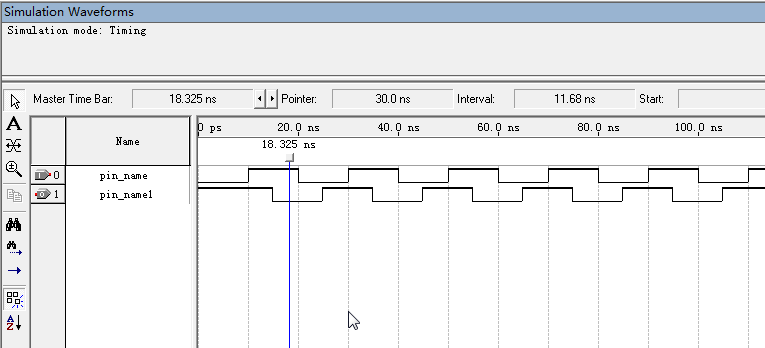

保存好仿真文件,就可以点蓝色三角按钮仿真。仿真结果如下,电路中的非门有10ns左右的延迟。

6、下载至板子

点击按钮

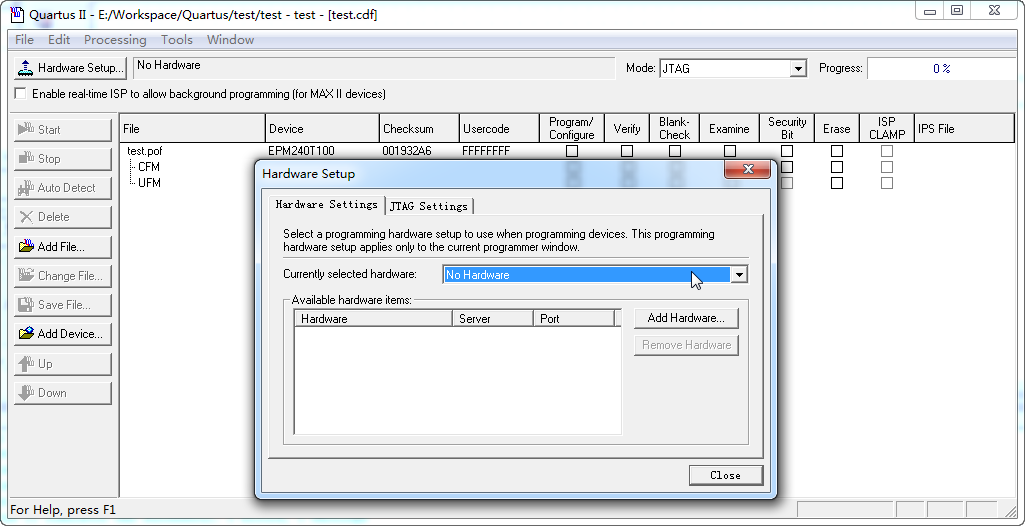

点击Hardware Setup选择USB-Blaster,并添加

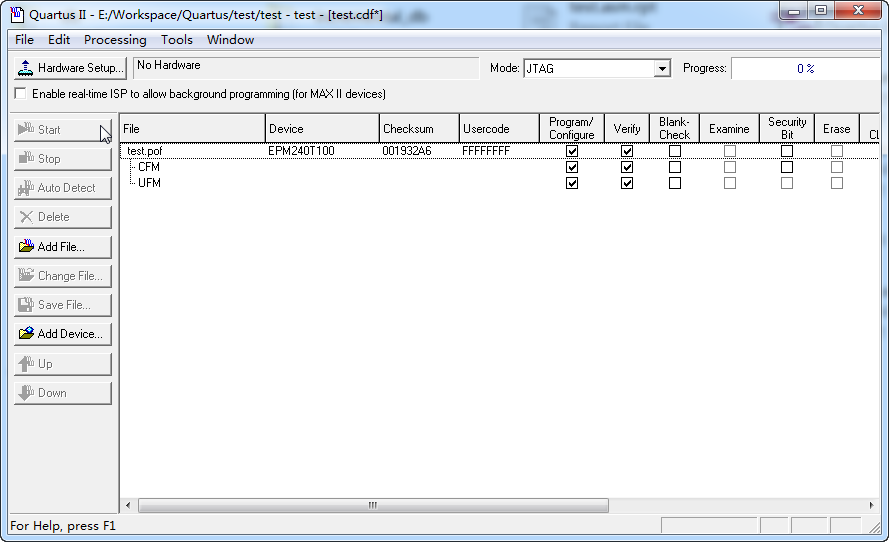

勾选前两项,然后点击Start下载,进度条至100%即下载成功。

7、导出模块

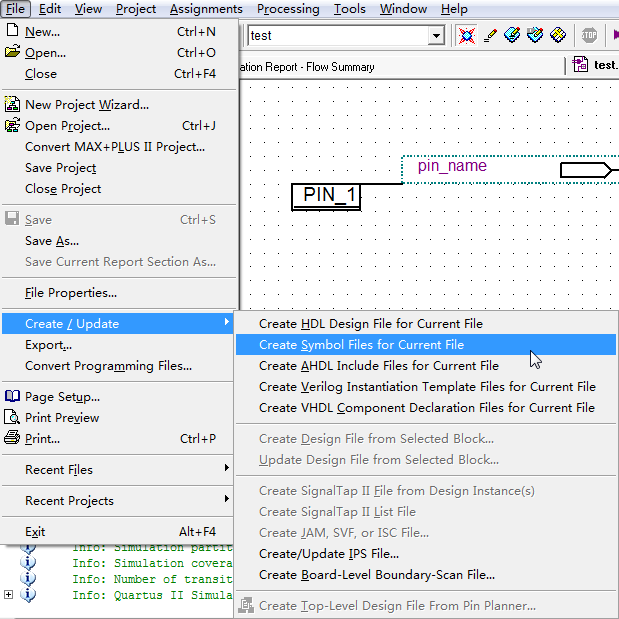

可选择菜单File --> Create/Update --> Create Symbol Files for Current File,将设计文件导出为模块。在设计文件Block Diagram(框图)中,可以像插入元件一样,插入设计好的模块。